## SSD202D UART/FUART Module Description

2022 SigmaStar Technology Corp. All rights reserved.

SigmaStar Technology makes no representations or warranties including, for example but not limited to, warranties of merchantability, fitness for a particular purpose, non-infringement of any intellectual property right or the accuracy or completeness of this document, and reserves the right to make changes without further notice to any products herein to improve reliability, function or design. No responsibility is assumed by SigmaStar Technology arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights, nor the rights of others.

SigmaStar is a trademark of SigmaStar Technology Corp. Other trademarks or names herein are only for identification purposes only and owned by their respective owners.

## 1. MODULE DESCRIPTION

#### 1.1. Overview

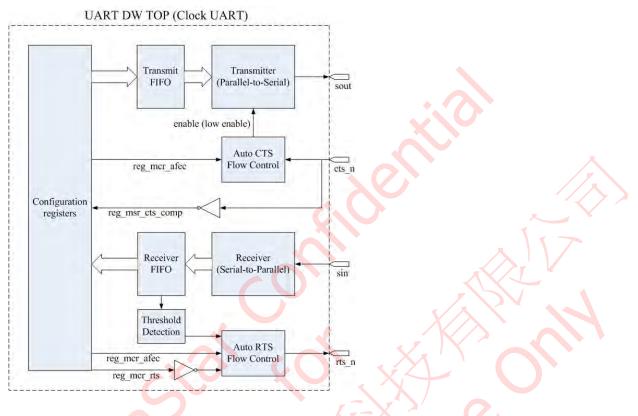

The UART module provides UART protocol to different devices. This ASIC provides two UART engines and one fast UART engine.

### 1.2. Function Description

The UART module has the following features:

- Supports 32-byte FIFO for read and write respectively

- Supports interrupt

- Supports auto flow control

## 1.3. Operating Mode

UART Protocol:

A character is composed of start bit (1 bit), data bit (5-8 bits), parity bit (1 or none) and stop bit (1, 1.5 or 2 bits).

Serial Data

Bit time

Start

Data Bits

S - 8

Parity

Stop

1, 1.5, 2

One Character

Block Diagram:

#### 1.3.1 UART Initialization

- Set interrupt control register

- Set FIFO control register

- Set line control register

- Set auto flow control (optional)

- Set baud rate

#### 1.3.2 UART Transmit or TX

- Write data to specified register to transmit characters

- Check line status register

- Get interrupt \_\_\_\_\_

#### 1.3.3 UART Receive or RX

- Read data from specified register to get received characters

- Check line status register

- Get interrupt

#### Note:

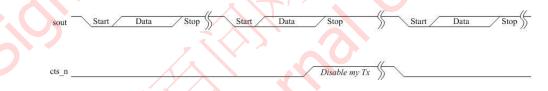

#### Auto Flow Control:

The "UART DW" can be configured to realize 16750-compatible Auto RTS/CTS serial data flow control mode.

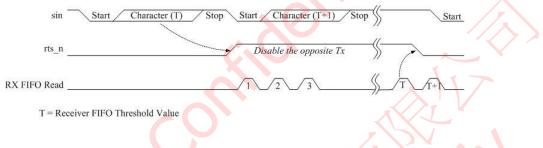

- Auto RTS:

- 1. Enable registers

- 2. Timing:

- a. The "rts\_n" output is pulled high (inactive) when the RX FIFO level reaches the threshold; this will keep the opposite UART from sending data.

- b. The "rts\_n" output is pulled low (active) when the RX FIFO becomes empty by reading RBR; this will signal the opposite UART to continue sending data.

- c. Character (T+1) may be received because "rts\_n" (high) was not detected before it entered the opposite UART's transmitter.

- Auto CTS:

- 1. Enable registers

- 2. Timing:

- a. The "cts\_n" input is pulled high (inactive); this will keep the transmitter from sending data.

- b. The "cts\_n" input is pulled low (active); this will enable the transmission to resume.

- c. If "cts\_n" input is not pulled high before the middle of the last "stop" bit, another character may be transmitted before the transmitter is disabled.

- d. While the transmitter is disabled, the TX FIFO can still be written and even become overflowed.

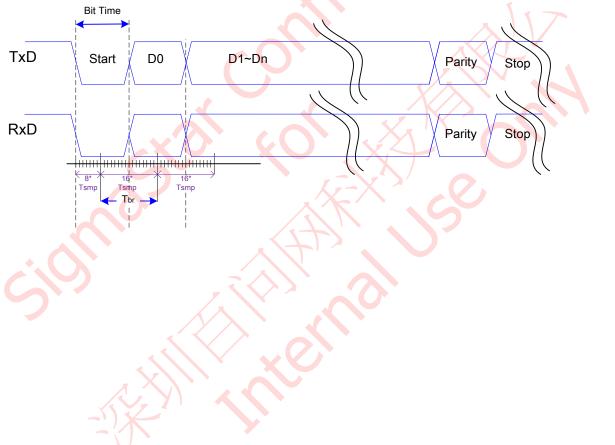

## 2. AC/DC SPECIFICATION

#### 2.1. AC Characteristics

| Parameter            | Symbol | Min Typ | Max | Unit |

|----------------------|--------|---------|-----|------|

| Baud Rate Period     | Tbr    | 115200  |     | bps  |

| UART Sampling Period | Tsmp   | 1/16    |     | Tbr  |

## 2.2. TxD/RxD Timing

## 3. REGISTER DESCRIPTION

## 3.1. FUART Register (Bank = 1102)

| FUART Regi           | ster (Bank = 1102) |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------------|--------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| l ndex<br>(Absolute) | Mnemonic           | Bit | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 00h                  | REG110200          | 7:0 | Default : 0x00 Access : R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| (110200h)            | THR_RBR_DLL[7:0]   | 7:0 | <ol> <li>When "reg_lcr_dl_access" = 0.</li> <li>Write: Transmitter Holding Register.</li> <li>Write transmit FIFO; note that writing data to a full<br/>FIFO results in the write data being lost.</li> <li>Read: Receiver Buffer.</li> <li>Read receive FIFO; note that any incoming data are<br/>lost when FIFO is full and an overrun error occurs.</li> <li>When "reg_lcr_dl_access" = 1.</li> <li>Divisor Latch LSB.</li> </ol>                                                                |

| 02h                  | REG110204          | 7:0 | Default : 0x00 Access : R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| (110204h)            | IER_DLH[7:0]       | 7:0 | <ol> <li>When "reg_lcr_dl_access" = 0.<br/>Interrupt Enable Registers (IER); 1: enabled.<br/>Bit [0]: Received Data Available Interrupt and<br/>Character Timeout Interrupt.<br/>Bit [1]: Transmitter Holding Register Empty Interrupt.<br/>Bit [2]: Receiver Line Status Interrupt.<br/>Bit [3]: Modem Status interrupt.<br/>Bit [7]: Programmable THRE Interrupt.</li> <li>When "reg_lcr_dl_access" = 1.<br/>Divisor Latch MSB.<br/>Baud rate = (serial clock freq.) / (16 * divisor).</li> </ol> |

| 04h                  | REG110208          | 7:0 | Default : 0x00 Access : R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| (110208h)            | FCR_IIR[7:0]       | 7:0 | <ol> <li>Write.</li> <li>FIFO Control Register (FCR).</li> <li>Bit [0]: FIFO enable.</li> <li>Bit [1]: write "1" to clear RX FIFO.</li> <li>Bit [2]: write "1" to clear TX FIFO.</li> <li>Bit [5:4]: Transmit FIFO Empty trigger level.</li> <li>"00": FIFO empty;</li> <li>"01": 2 characters in the FIFO;</li> <li>"10": FIFO 1/4 full;</li> <li>"11": FIFO 1/2 full.</li> </ol>                                                                                                                  |

| FUART Regi          | ster (Bank = 1102)  |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|---------------------|---------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Index<br>(Absolute) | Mnemonic            | Bit | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|                     |                     | 5   | Bit [7:6]: Receiver FIFO Interrupt trigger level.<br>"00": 1 character in the FIFO;<br>"01": FIFO 1/4 full;<br>"10": FIFO 1/2 full;<br>"11": FIFO 2 less than full.<br>2. Read.<br>Interrupt Identification Registers (IIR).<br>Bit [0]: 1: no interrupt is pending.<br>Bit [3:1]: interrupt identified.<br>"110": character timeout.<br>"011": Receiver Line Status.<br>"010": Receiver Data Available.<br>"001": Transmitter Holding Register empty.<br>"000": Modem Status. |  |

| 06h                 | REG11020C           | 7:0 | Default : 0x03 Access : R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| -                   | LCR_DL_ACCESS       | 7   | Divisor Latch Access.<br>1: The divisor latches can be accessed.                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|                     | LCR_BREAK_CTRL      | 6   | Break control bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|                     |                     | 5   | Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|                     | LCR_EVEN_PARITY_SEL | 4   | 1: Select even parity.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| •. C                | LCR_PARITY_EN       | 3   | 1: Generate parity bit on serial out.                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| 5                   | LCR_STOP_BITS       | 2   | Specify the number of stop bits.<br>"0": 1 stop bit;<br>"1": 1.5 stop bits when 5-bit character length is selected<br>and 2 bits otherwise.                                                                                                                                                                                                                                                                                                                                    |  |

|                     | LCR_CHAR_BITS[1:0]  | 1:0 | Select number of bits in each character.<br>"00": 5 bits; "01": 6 bits; "10": 7 bits; "11": 8 bits.                                                                                                                                                                                                                                                                                                                                                                            |  |

| 08h                 | REG110210           | 7:0 | Default : 0x00 Access : R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| (110210h)           | /                   | 7:6 | Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|                     | MCR_AFCE            | 5   | Auto Flow Control Enable; 1: enable.                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|                     | MCR_LOOPBACK        | 4   | 1: Loopback mode.<br>SOUT -> SIN (pad "STX_PAD_O" will be set to "1").<br>DTR -> DSR.<br>RTS-> CTS.<br>Out1 -> RI.<br>Out2 -> DCD.                                                                                                                                                                                                                                                                                                                                             |  |

|                     | MCR_OUT2            | 3   | In loopback mode, connect to Data Carrier Detect (DCD) signal input.                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| FUART Regi          | ster (Bank = 1102) |     |                                                                                                                                  |

|---------------------|--------------------|-----|----------------------------------------------------------------------------------------------------------------------------------|

| Index<br>(Absolute) | Mnemonic           | Bit | Description                                                                                                                      |

|                     | MCR_OUT1           | 2   | In loopback mode, connect to Ring Indicator (RI) signal input.                                                                   |

|                     | MCR_RTS            | 1   | Request To Send (RTS) signal control.<br>"0": RTS is "1"; "1": RTS is "0".                                                       |

|                     | MCR_DTR            | 0   | Data Terminal Ready (DTR) signal control.<br><b>"0":</b> DTR is "1"; <b>"1":</b> DTR is "0".                                     |

| 0Ah                 | REG110214          | 7:0 | Default : 0x00 Access : R0                                                                                                       |

| (110214h)           | LSR_ERROR          | 7   | Receiver FIFO Error bit.                                                                                                         |

|                     | LSR_TX_EMPTY       | 6   | 1: Transmitter (tx FIFO and shift registers) Empty<br>indicator.<br>Clear after writing data into tx FIFO.                       |

|                     | LSR_TXFIFO_EMPTY   | 5   | 1: Transmit FIFO is empty.<br>Clear after writing data into tx FIFO.<br>Generate a Transmitter Holding Register Empty interrupt. |

|                     | LSR_BI             | 4   | Break Interrupt bit.                                                                                                             |

|                     | LSR_FE             | 3   | 1: Framing Error indicator.<br>Clear when reading.<br>Generate a Receiver Line Status interrupt.                                 |

| -iC                 | LSR_PE             | 2   | 1: Parity Error indicator.<br>Clear when reading.<br>Generate a Receiver Line Status interrupt.                                  |

|                     | LSR_OE             | 1   | 1: RX Overrun Error indicator.<br>Clear when reading.<br>Generate a Receiver Line Status interrupt.                              |

|                     | LSR_DR             | 0   | 1: Received Data Ready indicator.                                                                                                |

| 0Ch                 | REG110218          | 7:0 | Default : 0x00 Access : R0                                                                                                       |

| (110218h)           | MSR_DCD_COMP       | 7   | Complement of "DCD" or equal to "OUT2" in loopback.                                                                              |

|                     | MSR_RI_COMP        | 6   | Complement of "RI" or equal to "OUT1" in loopback.                                                                               |

|                     | MSR_DSR_COMP       | 5   | Complement of "DSR" or equal to "DTR" in loopback.                                                                               |

|                     | MSR_CTS_COMP       | 4   | Complement of "CTS" or equal to "RTS" in loopback.                                                                               |

|                     | MSR_DDCD           | 3   | Delta Data Carrier Detect (DDCD) indicator.<br>"1": the "DCD" line has changed its state.<br>Clear when reading.                 |

|                     | MSR_TERI           | 2   | Trailing Edge of Ring Indictor (TERI) detector.<br>The "RI" line has changed its state from low to high.<br>Clear when reading.  |

| FUART Regi          | FUART Register (Bank = 1102) |     |                                                                                                                    |  |  |

|---------------------|------------------------------|-----|--------------------------------------------------------------------------------------------------------------------|--|--|

| Index<br>(Absolute) | Mnemonic                     | Bit | Description                                                                                                        |  |  |

|                     | MSR_DDSR                     | 1   | Delta Data Set Ready (DDSR) indicator.<br><b>"1": the "DSR" line has changed its state.</b><br>Clear when reading. |  |  |

|                     | MSR_DCTS                     | 0   | Delta Clear To Send (DCTS) indicator.<br>"1": the "CTS" line has changed its state.<br>Clear when reading.         |  |  |

| OEh                 | REG11021C                    | 7:0 | Default : 0x00 Access : R0                                                                                         |  |  |

| (11021Ch)           | -                            | 7:5 | Reserved.                                                                                                          |  |  |

|                     | USR_RFF                      | 4   | Rx FIFO Full.                                                                                                      |  |  |

|                     | USR_RFNE                     | 3   | Rx FIFO Not Empty.                                                                                                 |  |  |

|                     | USR_TFE                      | 2   | Tx FIFO Empty.                                                                                                     |  |  |

|                     | USR_TFNF                     | 1   | Tx FIFO Not Full.                                                                                                  |  |  |

|                     | USR_BUSY                     | 0   | UART Busy.                                                                                                         |  |  |

| 10h                 | REG110220                    | 7:0 | Default : 0x00 Access : RO                                                                                         |  |  |

| (110220h)           | -                            | 7:6 | Reserved.                                                                                                          |  |  |

|                     | TFL[5:0]                     | 5:0 | Tx FIFO level.                                                                                                     |  |  |

| 12h                 | REG110224                    | 7:0 | Default : 0x00 Access : RO                                                                                         |  |  |

| (110224h)           |                              | 7:6 | Reserved.                                                                                                          |  |  |

|                     | RFL[5:0]                     | 5:0 | Rx FIFO level.                                                                                                     |  |  |

# 3.2. UARTO Register (Bank = 1108)

| UARTO Regi          | UARTO Register (Bank = 1108) |     |                                                                                |                                                                                                                               |  |

|---------------------|------------------------------|-----|--------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|--|

| Index<br>(Absolute) | Mnemonic                     | Bit | Description                                                                    |                                                                                                                               |  |

| 00h                 | REG110800                    | 7:0 | Default : 0x00                                                                 | Access : R/W                                                                                                                  |  |

| (110800h)           | THR_RBR_DLL[7:0]             | 7:0 | FIFO results in the write<br>Read: Receiver Buffer.<br>Read receive FIFO; note | ng Register.<br>e that writing data to a full<br>data being lost.<br>that any incoming data are<br>d an overrun error occurs. |  |

| 02h                 | REG110804                    | 7:0 | Default : 0x00                                                                 | Access : R/W                                                                                                                  |  |

| UARTO Regi          | ster (Bank = 1108) |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------------------|--------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Index<br>(Absolute) | Mnemonic           | Bit | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| (110804h)           | IER_DLH[7:0]       | 7:0 | <ol> <li>When "reg_lcr_dl_access" = 0.<br/>Interrupt Enable Registers (IER); 1: enabled.<br/>Bit [0]: Received Data Available Interrupt and<br/>Character Timeout Interrupt.<br/>Bit [1]: Transmitter Holding Register Empty Interrupt.<br/>Bit [2]: Receiver Line Status Interrupt.<br/>Bit [3]: Modem Status interrupt.<br/>Bit [3]: Modem Status interrupt.<br/>Bit [7]: Programmable THRE Interrupt.</li> <li>When "reg_lcr_dl_access" = 1.<br/>Divisor Latch MSB.<br/>Baud rate = (serial clock freq.) / (16 * divisor).</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 04h                 | REG110808          | 7:0 | Default : 0x00 Access : R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| (110808h)           | FCR_IIR[7:0]       | 7:0 | <ol> <li>Write.         FIFO Control Register (FCR).         Bit [0]: FIFO enable.         Bit [1]: write "1" to clear RX FIFO.         Bit [2]: write "1" to clear TX FIFO.         Bit [2]: write "1" to clear TX FIFO.         Bit [5:4]: Transmit FIFO Empty trigger level.         "00": FIFO empty:         "01": 2 characters in the FIFO;         "10": FIFO 1/4 full;         "11": FIFO 1/2 full.         Bit [7:6]: Receiver FIFO Interrupt trigger level.         "00": 1 character in the FIFO;         "01": FIFO 1/4 full;         "10": FIFO 1/4 full;         "10": FIFO 1/4 full;         "10": FIFO 1/2 full.         Bit [7:6]: Receiver FIFO Interrupt trigger level.         "00": 1 character in the FIFO;         "01": FIFO 1/2 full;         "11": FIFO 1/2 full;         "11": FIFO 2 less than full.         2. Read.         Interrupt Identification Registers (IIR).         Bit [0]: 1: no interrupt is pending.         Bit [3:1]: interrupt identified.         "10": Receiver Line Status.         "01": Receiver Data Available.         "001": Transmitter Holding Register empty.         "000": Modem Status.         "00": Modem Status.         "0"         "0"         "0"         "0"         "0"         "0"         "0"         "0"         "0"         "0"         "0"         "0"         "</li></ol> |

| 06h                 | REG11080C          | 7:0 | Default : 0x03 Access : R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| (11080Ch)           | LCR_DL_ACCESS      | 7   | Divisor Latch Access; 1: The divisor latches can be accessed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                     | LCR_BREAK_CTRL     | 6   | Break control bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| UARTO Regi          | ster (Bank = 1108)  |     |                                                                                                                                             |

|---------------------|---------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------|

| Index<br>(Absolute) | Mnemonic            | Bit | Description                                                                                                                                 |

|                     | -                   | 5   | Reserved.                                                                                                                                   |

|                     | LCR_EVEN_PARITY_SEL | 4   | 1: Select even parity.                                                                                                                      |

|                     | LCR_PARITY_EN       |     | 1: Generate parity bit on serial out.                                                                                                       |

|                     | LCR_STOP_BITS       | 2   | Specify the number of stop bits.<br>"0": 1 stop bit;<br>"1": 1.5 stop bits when 5-bit character length is selected<br>and 2 bits otherwise. |

|                     | LCR_CHAR_BITS[1:0]  | 1:0 | Select number of bits in each character.<br>"00": 5 bits; "01": 6 bits; "10": 7 bits; "11": 8 bits.                                         |

| 08h                 | REG110810           | 7:0 | Default : 0x00 Access : R/W                                                                                                                 |

| (110810h)           | -                   | 7:6 | Reserved.                                                                                                                                   |

|                     | MCR_AFCE            | 5   | Auto Flow Control Enable; 1: enable.                                                                                                        |

| Ν                   | MCR_LOOPBACK        | 4   | 1: Loopback mode.<br>SOUT -> SIN (pad "STX_PAD_O" will be set to "1").<br>DTR -> DSR.<br>RTS-> CTS.<br>Out1 -> RI.<br>Out2 -> DCD.          |

|                     | MCR_OUT2            | 3   | In loopback mode, connect to Data Carrier Detect (DCD) signal input.                                                                        |

| cil                 | MCR_OUT1            | 2   | In loopback mode, connect to Ring Indicator (RI) signal input.                                                                              |

|                     | MCR_RTS             | 1   | Request To Send (RTS) signal control.<br>"0": RTS is "1"; "1": RTS is "0".                                                                  |

|                     | MCR_DTR             | 0   | Data Terminal Ready (DTR) signal control.<br>"0": DTR is "1"; "1": DTR is "0".                                                              |

| 0Ah                 | REG110814           | 7:0 | Default : 0x00 Access : R0                                                                                                                  |

| (110814h)           | LSR_ERROR           | 7   | Receiver FIFO Error bit.                                                                                                                    |

|                     | LSR_TX_EMPTY        | 6   | 1: Transmitter (tx FIFO and shift registers) Empty<br>indicator.<br>Clear after writing data into tx FIFO.                                  |

|                     | LSR_TXFIFO_EMPTY    | 5   | 1: Transmit FIFO is empty.<br>Clear after writing data into tx FIFO.<br>Generate a Transmitter Holding Register Empty interrupt.            |

|                     | LSR_BI              | 4   | Break Interrupt bit.                                                                                                                        |

|                     | LSR_FE              | 3   | 1: Framing Error indicator.                                                                                                                 |

| UARTO Regi          | ster (Bank = 1108) | <del>,                                     </del> | r                                                                                                                                |  |

|---------------------|--------------------|---------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--|

| Index<br>(Absolute) | Mnemonic           | Bit                                               | Description                                                                                                                      |  |

|                     |                    |                                                   | Clear when reading.                                                                                                              |  |

|                     |                    |                                                   | Generate a Receiver Line Status interrupt.                                                                                       |  |

|                     | LSR_PE             | 2                                                 | 1: Parity Error indicator.<br>Clear when reading.<br>Generate a Receiver Line Status interrupt.                                  |  |

|                     | LSR_OE             | 1                                                 | 1: RX Overrun Error indicator.<br>Clear when reading.<br>Generate a Receiver Line Status interrupt.                              |  |

|                     | LSR_DR             | 0                                                 | 1: Received Data Ready indicator.                                                                                                |  |

| OCh                 | REG110818          | 7:0                                               | Default : 0x00 Access : R0                                                                                                       |  |

| (110818h)           | MSR_DCD_COMP       | 7                                                 | Complement of "DCD" or equal to "OUT2" in loopback.                                                                              |  |

|                     | MSR_RI_COMP        | 6                                                 | Complement of "RI" or equal to "OUT1" in loopback.                                                                               |  |

|                     | MSR_DSR_COMP       | 5                                                 | Complement of "DSR" or equal to "DTR" in loopback.                                                                               |  |

|                     | MSR_CTS_COMP       | 4                                                 | Complement of "CTS" or equal to "RTS" in loopback.                                                                               |  |

| -                   | MSR_DDCD           | 3                                                 | Delta Data Carrier Detect (DDCD) indicator.<br>"1": the "DCD" line has changed its state.<br>Clear when reading.                 |  |

|                     | MSR_TERI           | 2                                                 | Trailing Edge of Ring Indicator (TERI) detector.<br>The "RI" line has changed its state from low to high.<br>Clear when reading. |  |

|                     | MSR_DDSR           |                                                   | Delta Data Set Ready (DDSR) indicator.<br>"1": the "DSR" line has changed its state.<br>Clear when reading.                      |  |

|                     | MSR_DCTS           | 0                                                 | Delta Clear To Send (DCTS) indicator.<br>"1": the "CTS" line has changed its state.<br>Clear when reading.                       |  |

| OEh                 | REG11081C          | 7:0                                               | Default : 0x00 Access : RO                                                                                                       |  |

| (11081Ch)           | /                  | 7:5                                               | Reserved.                                                                                                                        |  |

|                     | USR_RFF            | 4                                                 | Rx FIFO Full.                                                                                                                    |  |

|                     | USR_RFNE           | 3                                                 | Rx FIFO Not Empty.                                                                                                               |  |

|                     | USR_TFE            | 2                                                 | Tx FIFO Empty.                                                                                                                   |  |

|                     | USR_TFNF           | 1                                                 | Tx FIFO Not Full.                                                                                                                |  |

|                     | USR_BUSY           | 0                                                 | UART Busy.                                                                                                                       |  |

| 10h                 | REG110820          | 7:0                                               | Default : 0x00 Access : RO                                                                                                       |  |

| (110820h)           | -                  | 7:6                                               | Reserved.                                                                                                                        |  |

|                     | TFL[5:0]           | 5:0                                               | Tx FIFO level.                                                                                                                   |  |

| UARTO Regi          | UARTO Register (Bank = 1108) |     |                |             |  |  |

|---------------------|------------------------------|-----|----------------|-------------|--|--|

| Index<br>(Absolute) | Mnemonic                     | Bit | Description    |             |  |  |

| 12h                 | REG110824                    | 7:0 | Default : 0x00 | Access : RO |  |  |

| (110824h)           | -                            | 7:6 | Reserved.      |             |  |  |

|                     | RFL[5:0]                     | 5:0 | Rx FIFO level. |             |  |  |

## 3.3. UART1 Register (Bank = 1109)

| UART1 Regi          | ster (Bank = 1109) |     |                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                    |

|---------------------|--------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| Index<br>(Absolute) | Mnemonic           | Bit | Description                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                    |

| 00h                 | REG110900          | 7:0 | Default : 0x00                                                                                                                                                                                                                                                                                                                                   | Access : R/W                                                                                                                                       |

| (110900h)           | THR_RBR_DLL[7:0]   | 7:0 | FIFO results in the write<br>Read: Receiver Buffer.<br>Read receive FIFO; note<br>lost when FIFO is full and                                                                                                                                                                                                                                     | ng Register.<br>e that writing data to a full<br>data being lost.<br>that any incoming data are<br>d an overrun error occurs.                      |

|                     | 2                  |     | 2. When "reg_lcr_dl_access<br>Divisor Latch LSB.                                                                                                                                                                                                                                                                                                 | " = 1.                                                                                                                                             |

| 02h                 | REG110904          | 7:0 | Default : 0x00                                                                                                                                                                                                                                                                                                                                   | Access : R/W                                                                                                                                       |

| (110904h)           | IER_DLH[7:0]       | 7:0 | <ol> <li>When "reg_lcr_dl_access<br/>Interrupt Enable Register<br/>Bit [0]: Received Data Av<br/>Character Timeout Interr<br/>Bit [1]: Transmitter Holdi<br/>Bit [2]: Receiver Line Sta<br/>Bit [3]: Modem Status in<br/>Bit [7]: Programmable Th<br/>2. When "reg_lcr_dl_access<br/>Divisor Latch MSB.<br/>Baud rate = (serial clock</li> </ol> | rs (IER); 1: enabled.<br>vailable Interrupt and<br>upt.<br>ing Register Empty Interrupt.<br>tus Interrupt.<br>terrupt.<br>HRE Interrupt.<br>" = 1. |

| 04h                 | REG110908          | 7:0 | Default : 0x00                                                                                                                                                                                                                                                                                                                                   | Access : R/W                                                                                                                                       |

| (110908h)           | FCR_IIR[7:0]       | 7:0 | <ol> <li>Write.</li> <li>FIFO Control Register (FOBit [0]: FIFO enable.</li> <li>Bit [1]: write "1" to clear</li> <li>Bit [2]: write "1" to clear</li> <li>Bit [5:4]: Transmit FIFO</li> <li>"00": FIFO empty;</li> </ol>                                                                                                                        | RX FIFO.<br>TX FIFO.                                                                                                                               |

| UART1 Regi          | ster (Bank = 1109)  | r           | r                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|---------------------|---------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Index<br>(Absolute) | Mnemonic            | Bit         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|                     |                     | 9<br>9<br>8 | <ul> <li>"01": 2 characters in the FIFO;</li> <li>"10": FIFO 1/4 full;</li> <li>"11": FIFO 1/2 full.</li> <li>Bit [7:6]: Receiver FIFO Interrupt trigger level.</li> <li>"00": 1 character in the FIFO;</li> <li>"01": FIFO 1/4 full;</li> <li>"10": FIFO 1/2 full;</li> <li>"11": FIFO 2 less than full.</li> <li>2. Read.</li> <li>Interrupt Identification Registers (IIR).</li> <li>Bit [0]: 1: no interrupt is pending.</li> <li>Bit [3:1]: interrupt identified.</li> <li>"11": Receiver Line Status.</li> <li>"010": Receiver Data Available.</li> <li>"00": Modem Status.</li> </ul> |  |  |

| 06h                 | REG11090C           | 7:0         | Default : 0x03 Access : R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| (110000)            | LCR_DL_ACCESS       | 7           | Divisor Latch Access.<br>1: The divisor latches can be accessed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

|                     | LCR_BREAK_CTRL      | 6           | Break control bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|                     |                     | 5           | Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| 5                   | LCR_EVEN_PARITY_SEL | 4           | 1: Select even parity.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|                     | LCR_PARITY_EN       | 3           | 1: Generate parity bit on serial out.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|                     | LCR_STOP_BITS       | 2           | Specify the number of stop bits.<br>"0": 1 stop bit;<br>"1": 1.5 stop bits when 5-bit character length is selected<br>and 2 bits otherwise.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|                     | LCR_CHAR_BITS[1:0]  | 1:0         | Select number of bits in each character.<br>"00": 5 bits; "01": 6 bits; "10": 7 bits; "11": 8 bits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| 08h                 | REG110910           | 7:0         | Default : 0x00 Access : R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| (110910h)           | -                   | 7:6         | Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|                     | MCR_AFCE            | 5           | Auto Flow Control Enable; 1: enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|                     | MCR_LOOPBACK        | 4           | 1: Loopback mode.<br>SOUT -> SIN (pad "STX_PAD_O" will be set to "1").<br>DTR -> DSR.<br>RTS-> CTS.<br>Out1 -> RI.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| UART1 Regi                                                                         | ister (Bank = 1109) |                                                                                |                                                                                                                  |  |  |

|------------------------------------------------------------------------------------|---------------------|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--|--|

| Index<br>(Absolute)                                                                | Mnemonic            | Bit                                                                            | Description                                                                                                      |  |  |

|                                                                                    |                     |                                                                                | Out2 -> DCD.                                                                                                     |  |  |

|                                                                                    | MCR_OUT2            | 3                                                                              | In loopback mode, connect to Data Carrier Detect (DCD) signal input.                                             |  |  |

|                                                                                    | MCR_OUT1            | 2                                                                              | In loopback mode, connect to Ring Indicator (RI) signal input.                                                   |  |  |

|                                                                                    | MCR_RTS             | 1                                                                              | Request To Send (RTS) signal control.<br>"0": RTS is "1"; "1": RTS is "0".                                       |  |  |

| MCR_DTR 0 Data Terminal Ready (DTR) signal co<br>"0": DTR is "1"; "1": DTR is "0". |                     | Data Terminal Ready (DTR) signal control.<br>"0": DTR is "1"; "1": DTR is "0". |                                                                                                                  |  |  |

| 0Ah                                                                                | REG110914           | 7:0                                                                            | Default : 0x00 Access : R0                                                                                       |  |  |

| (110914h)                                                                          | LSR_ERROR           | 7                                                                              | Receiver FIFO Error bit.                                                                                         |  |  |

|                                                                                    | LSR_TX_EMPTY        | 6                                                                              | 1: Transmitter (tx FIFO and shift registers) Empty<br>indicator.<br>Clear after writing data into tx FIFO.       |  |  |

|                                                                                    | LSR_TXFIFO_EMPTY    | 5                                                                              | 1: Transmit FIFO is empty.                                                                                       |  |  |

|                                                                                    | S                   |                                                                                | Clear after writing data into tx FIFO.<br>Generate a Transmitter Holding Register Empty interrupt.               |  |  |

|                                                                                    | LSR_BI              | 4                                                                              | Break Interrupt bit.                                                                                             |  |  |

| ~ C                                                                                | LSR_FE              | 3                                                                              | 1: Framing Error indicator.<br>Clear when reading.<br>Generate a Receiver Line Status interrupt.                 |  |  |

|                                                                                    | LSR_PE              | 2                                                                              | 1: Parity Error indicator.<br>Clear when reading.<br>Generate a Receiver Line Status interrupt.                  |  |  |

|                                                                                    | LSR_OE              | 1                                                                              | 1: RX Overrun Error indicator.<br>Clear when reading.<br>Generate a Receiver Line Status interrupt.              |  |  |

|                                                                                    | LSR_DR              | 0                                                                              | 1: Received Data Ready indicator.                                                                                |  |  |

| 0Ch                                                                                | REG110918           | 7:0                                                                            | Default : 0x00 Access : R0                                                                                       |  |  |

| (110918h)                                                                          | MSR_DCD_COMP        | 7                                                                              | Complement of "DCD" or equal to "OUT2" in loopback.                                                              |  |  |

|                                                                                    | MSR_RI_COMP         | 6                                                                              | Complement of "RI" or equal to "OUT1" in loopback.                                                               |  |  |

|                                                                                    | MSR_DSR_COMP        | 5                                                                              | Complement of "DSR" or equal to "DTR" in loopback.                                                               |  |  |

|                                                                                    | MSR_CTS_COMP        | 4                                                                              | Complement of "CTS" or equal to "RTS" in loopback.                                                               |  |  |

|                                                                                    | MSR_DDCD            | 3                                                                              | Delta Data Carrier Detect (DDCD) indicator.<br>"1": the "DCD" line has changed its state.<br>Clear when reading. |  |  |

| UART1 Regi          | UART1 Register (Bank = 1109) |     |                                                                                                                                  |  |  |  |

|---------------------|------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Index<br>(Absolute) | Mnemonic                     | Bit | Description                                                                                                                      |  |  |  |

|                     | MSR_TERI                     | 2   | Trailing Edge of Ring Indicator (TERI) detector.<br>The "RI" line has changed its state from low to high.<br>Clear when reading. |  |  |  |

|                     | MSR_DDSR                     | 1   | Delta Data Set Ready (DDSR) indicator.<br>"1": the "DSR" line has changed its state.<br>Clear when reading.                      |  |  |  |

|                     | MSR_DCTS                     | 0   | Delta Clear To Send (DCTS) indicator.<br>"1": the "CTS" line has changed its state.<br>Clear when reading.                       |  |  |  |

| OEh                 | REG11091C                    | 7:0 | Default : 0x00 Access : RO                                                                                                       |  |  |  |

| (11091Ch)           |                              | 7:5 | Reserved.                                                                                                                        |  |  |  |

|                     | USR_RFF                      | 4   | Rx FIFO Full.                                                                                                                    |  |  |  |

|                     | USR_RFNE                     | 3   | Rx FIFO Not Empty                                                                                                                |  |  |  |

|                     | USR_TFE                      | 2   | Tx FIFO Empty.                                                                                                                   |  |  |  |

|                     | USR_TFNF                     | 1   | Tx FIFO Not Full.                                                                                                                |  |  |  |

|                     | USR_BU <mark>S</mark> Y      | 0   | UART Busy.                                                                                                                       |  |  |  |

| 10h                 | REG110920                    | 7:0 | Default : 0x00 Access : RO                                                                                                       |  |  |  |

| (110920h)           |                              | 7:6 | Reserved.                                                                                                                        |  |  |  |